안녕하세요!

오늘 저는 반도체 프로세스 및 애플리케이션의 네트워킹에 대해 글을 쓰고 있습니다!

오늘 포스팅은 공식은 없지만 내용과 사진이 많아서 글이 길어질 것 같아요..!

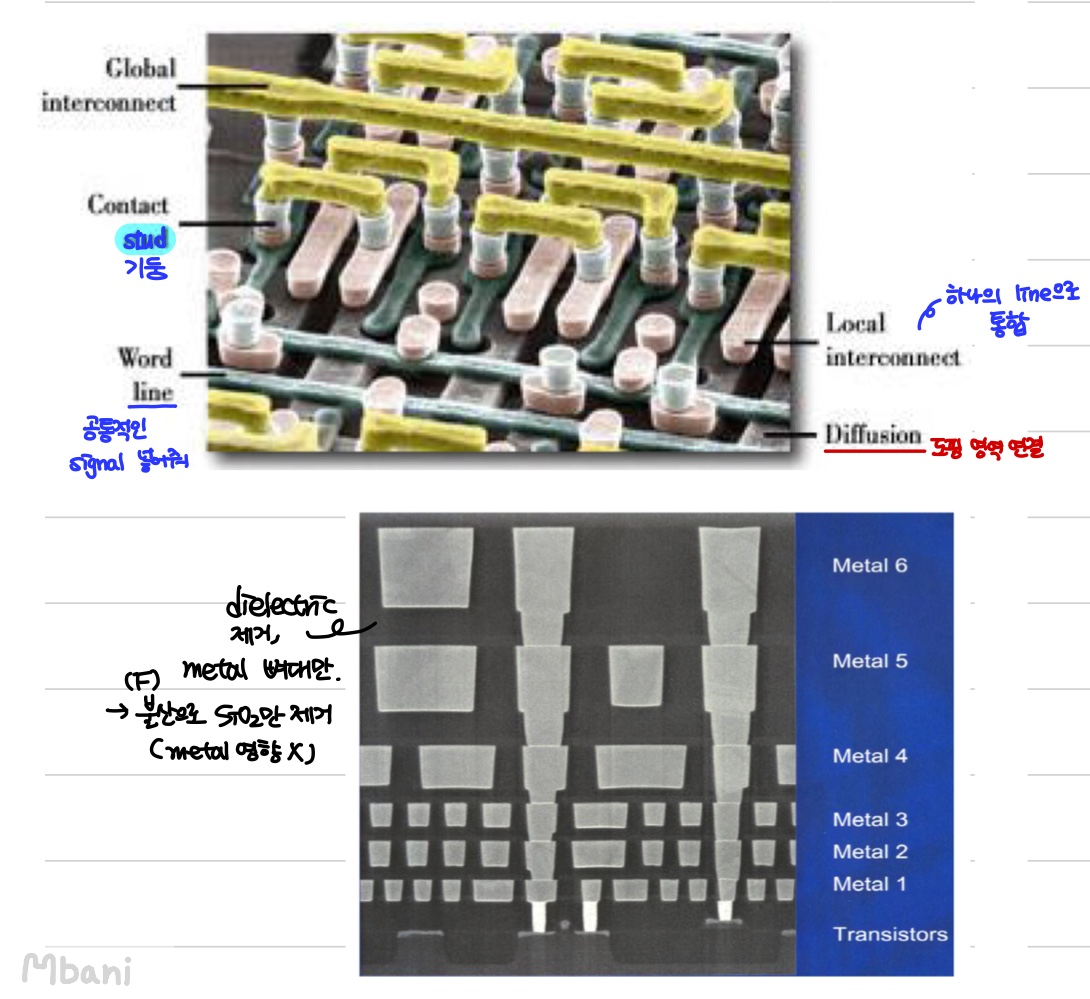

- IC 칩의 연결

연결은 다음과 같이 IC 칩에 적용됩니다.

IC에 사용되는 일반적인 인터커넥트 재료에는 세 가지 유형이 있습니다.

– 알 : 쉬운 눕힘, 쉬운 조립, 쉬운 식각

– 폴리-Si : Si와 WorkFunction의 차이가 작고 ohmic contact이 작기 때문에 손실이 적다.

– 확산 영역 : 같은 부위에 도핑

용도에 따라 각각 교차하다밀도 향상이 목표입니다.

이러한 연결 재료는 낮은 표면 저항가질 필요가

전압 강하 및 전파 지연을 최소화하여 RC 지연 최소화 당신이해야하기 때문에

그리고 줄을 분리 SiO2와 반응성이 없어야 하며 낮은 R 저항 접촉이 필요합니다.에게.

장기간 운영해야 하므로 효율성, 내구성, 제작이 중요합니다.

- 금속 연결 및 접촉 기술

기술의 발전에 따라 위의 세 가지 화합물에 사용되는 재료도 변경되었습니다.

– Gate Metal: Au/Al -> Poly-Si -> 종속적 Poly-Si -> Polycide 또는 Silicide

– 접속금속 : Al -> AlCu / Cu

– 장벽 금속: TiN(Al/Si) -> TiW(Al/실리사이드), TaN(Cu/low-k 유전체)

각 물질에 대해 알아보자!

¤ 금: 높은 확산성과 우수한 전도도를 가지며 Si에서 깊은 수준의 재결합 중심을 생성합니다.

에너지 밴드 갭 내에서 재결합 중심이 나타나면 e-가 갇히고 시간이 지남에 따라 h+를 만나 재결합합니다.

– 자유 라디칼의 수명을 줄입니다.

– 칩 패키징에 널리 사용

¤ Al: 저렴하고 낮은 저항, 우수한 전도성, SiO2에 대한 우수한 접착력

– 연결 스파이크 및 일렉트로마이그레이션 문제있다

¤ Poly-Si : 안정성이 좋고, P, Antimony, Doping 가능

– 비저항이 감소하여 접촉문제가 없고 저항이 거의 없음

– 전도성이 낮고 성형이 어렵고 속도가 느림

¤ 실리사이드: 금속(TiSi2, CoSi), 안정한 금속과 반도체의 결합

– 낮은 저항률, 우수한 열 안정성

– 게이트 전극으로 사용 가능

¤ 구리: 낮은 저항률, 적은 일렉트로마이그레이션

– SiO2 접착력이 떨어져 전기적으로 분리가 어려운 식각 문제가 있다.

– 다마신 공정용도(Cu, low-k 유전체의 접속)

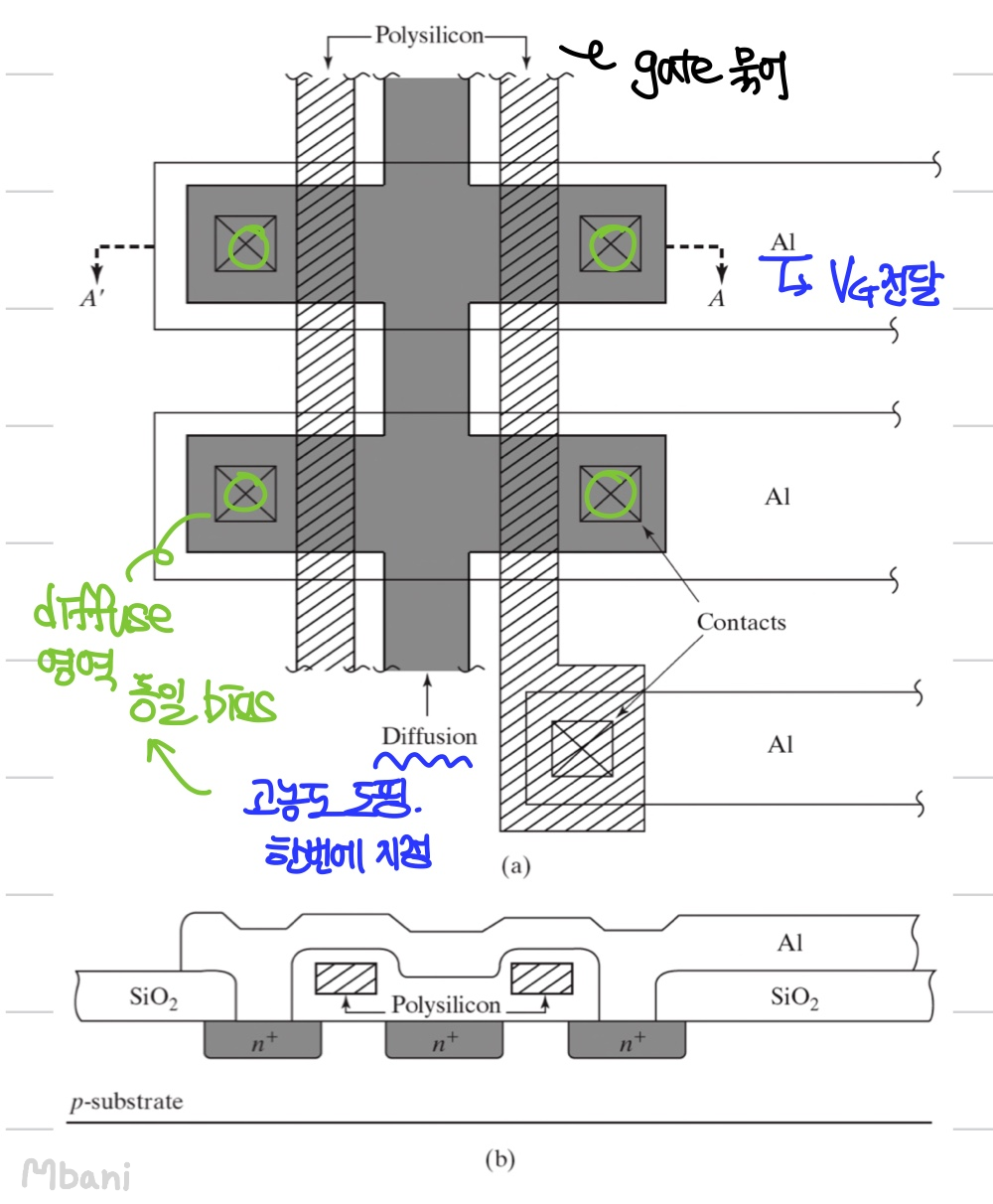

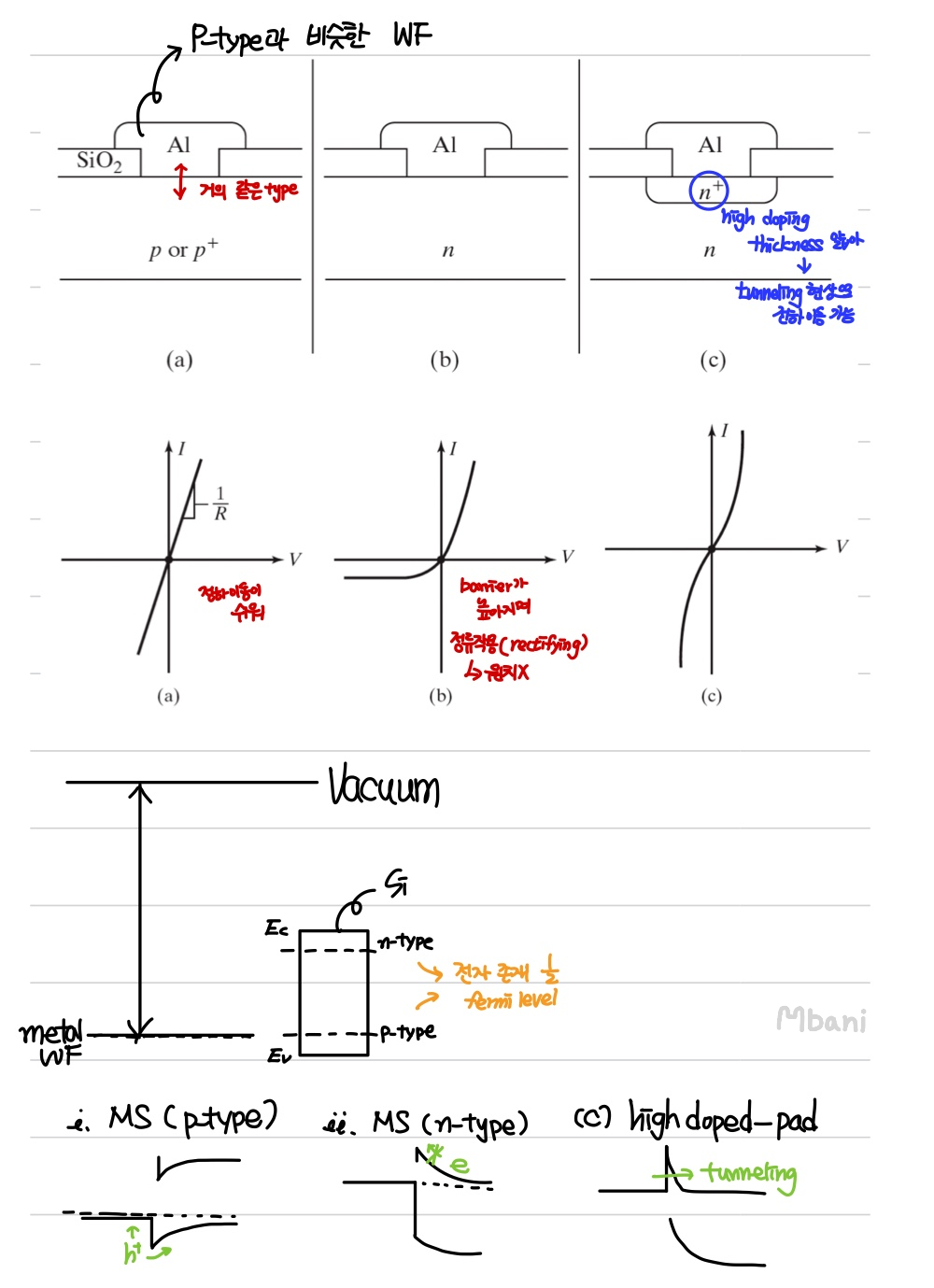

- 옴 접촉 형성

자세한 오믹컨택은 아래 이미지와 물리전자 포스팅에서 확인해주세요!

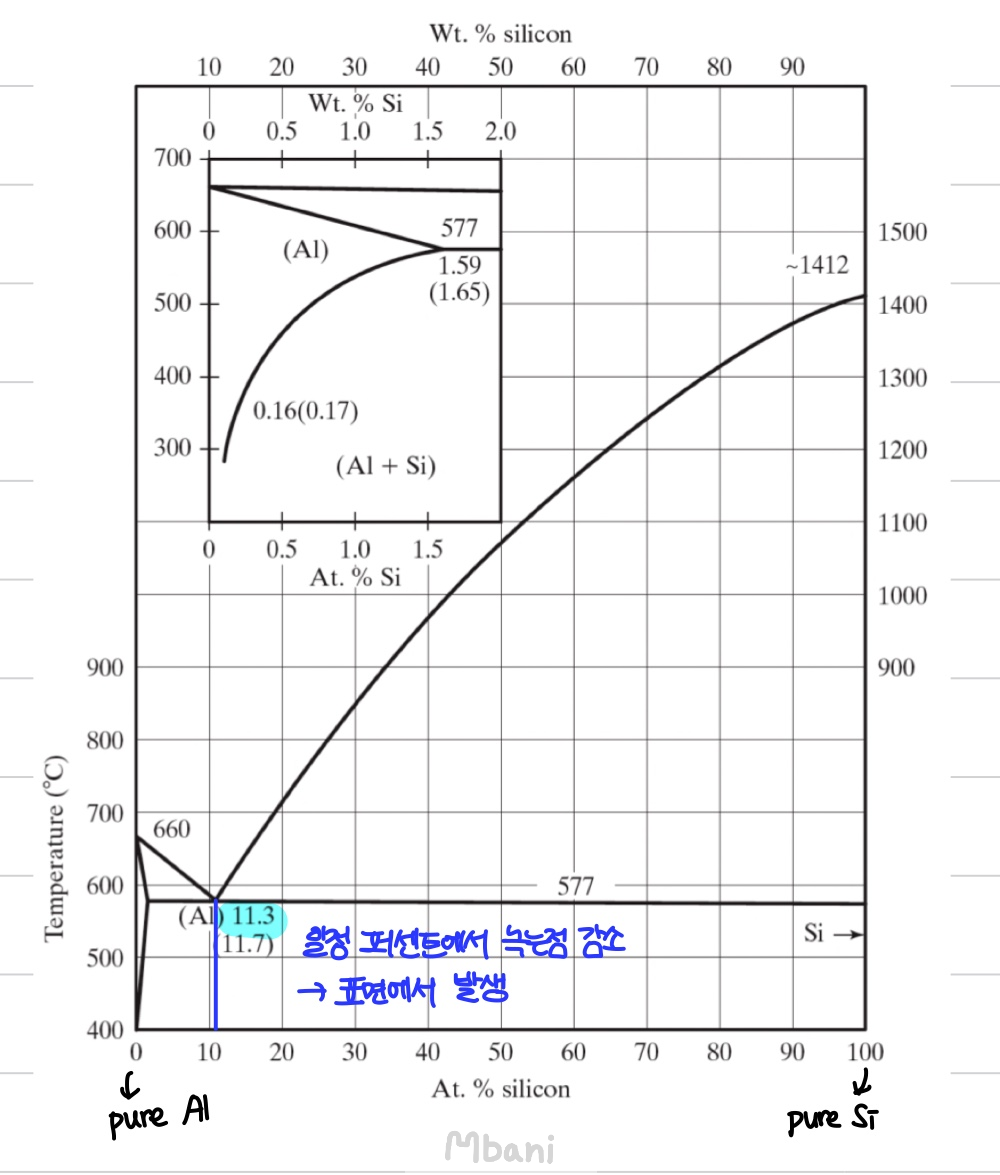

< Aluminium-Silizium-Eutektikum >

- 모든 행동

Si는 1412℃에서 녹고 순수한 Al은 660℃에서 녹는점을 가집니다.

Si와 Al을 섞으면 공융 속성 => T_melt < 660℃해야한다

Al-88.7%와 Si-11.3%를 포함할 때 최소 용융온도(공융)는 577℃이다.

결과적으로, 모든 고온 공정 후 공정 계속당신은해야합니다!

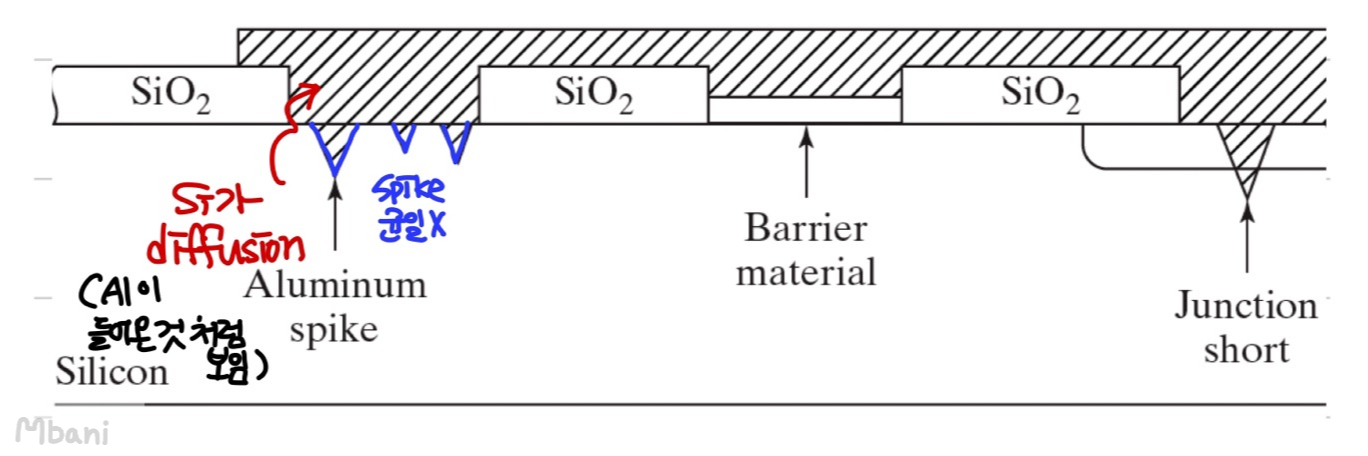

- 알루미늄 스파이크 및 접합부 관통

일반적으로 접촉 형성을 개선하기 위해 Al은 450~500℃의 불활성 분위기에서 어닐링됩니다.수입.

이때 Si와 Al의 반응성이 좋다. Si에서 Al로의 확산현상이 발생합니다.

얕은 접합의 경우 Si 위에 Al 컨택이 형성되며 Si 흡수량은 시간, 온도, 컨택 크기에 따라 달라집니다.

이 불균일한 흡수 현상 페네트레이트 알 스파이크 & 시 호출됩니다.

그리고 n형 Si를 사용하는 경우 다음과 같은 문제가 발생한다.

① 표면적 증가로 인해 IV 커브 예측이 어려움

② 표면적이 커질수록 R이 커져 곡선이 하강한다.

③ 고농도의 표면 도핑으로 인해 ohmic이 깨져 물성이 변화됨

이러한 문제를 해결하는 방법

① 증착 시 Al 필름에 1% Si 추가

-> 확산은 농도의 차이로 인해 발생하므로 Si를 첨가하면 이 차이가 줄어듭니다.

② 폴리실리콘 박막 또는 금속(TiN, Pt, W)으로 증착 장벽층을 형성합니다.해

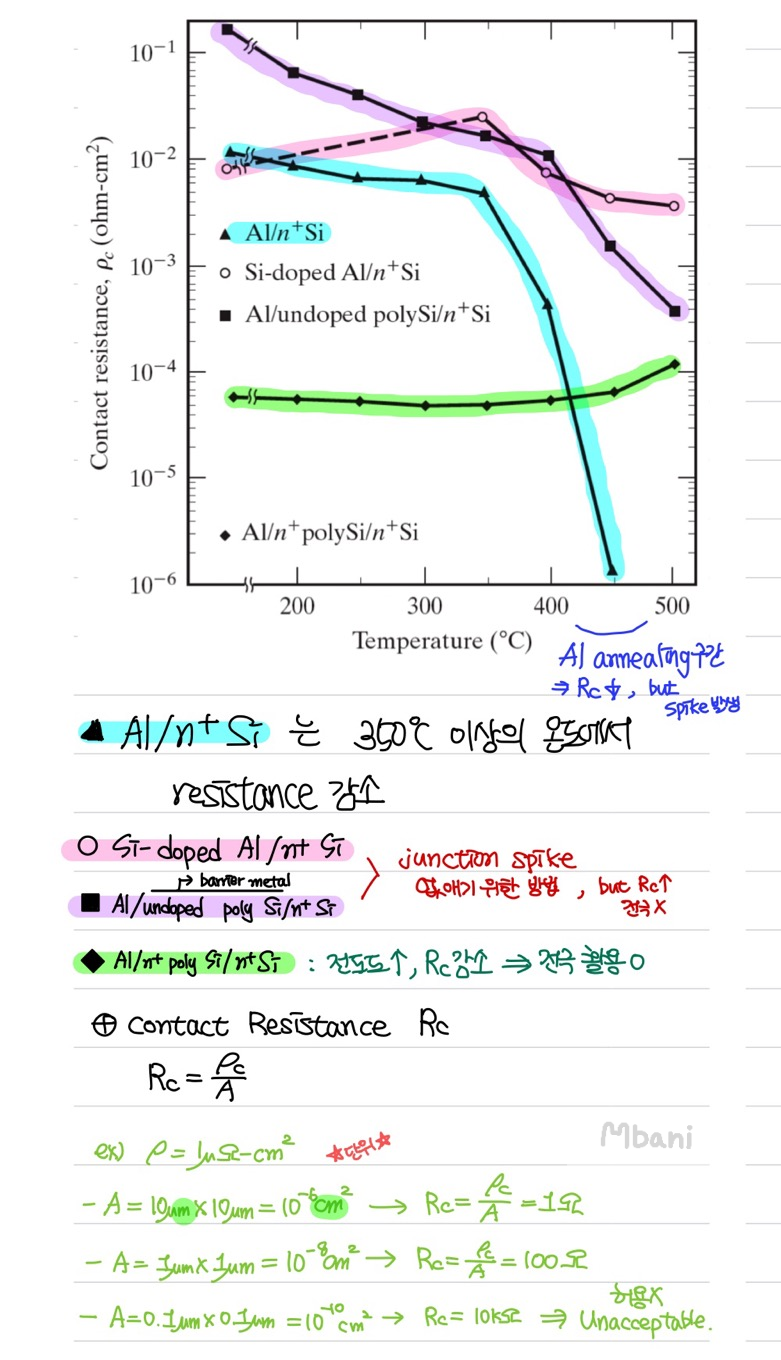

- 접촉 저항

접촉 저항이 낮을수록 두 재료 사이의 옴 접촉과 관련된 저항이 작습니다.

아래 다이어그램은 재료 간의 저항을 보여줍니다.

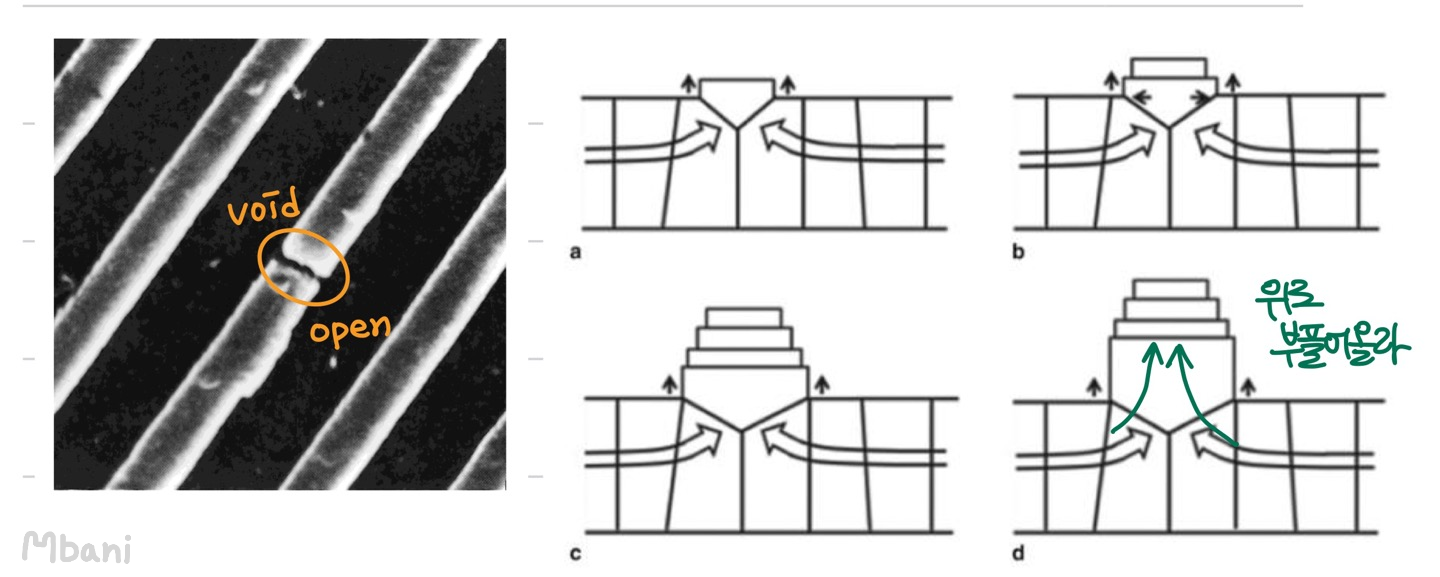

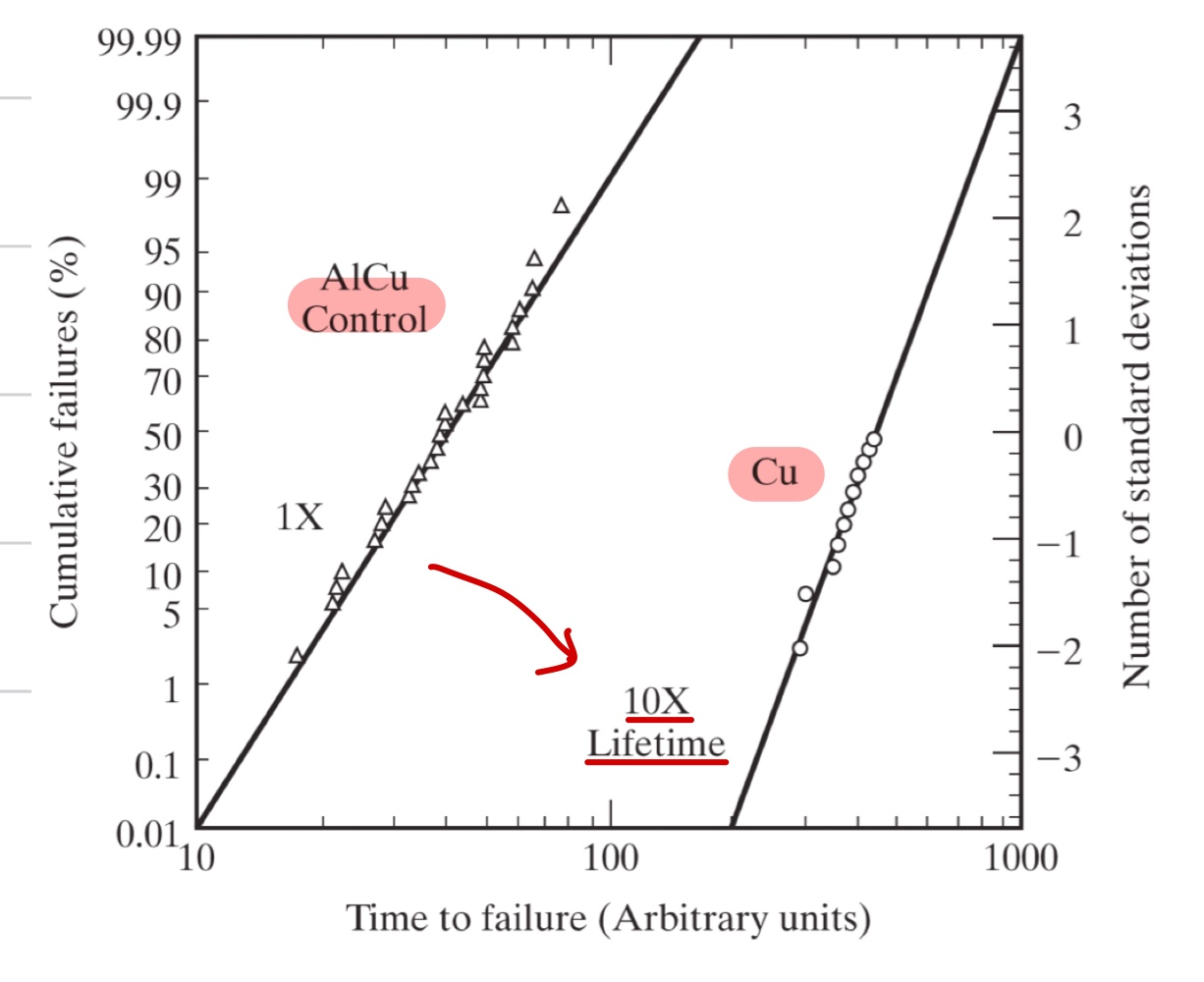

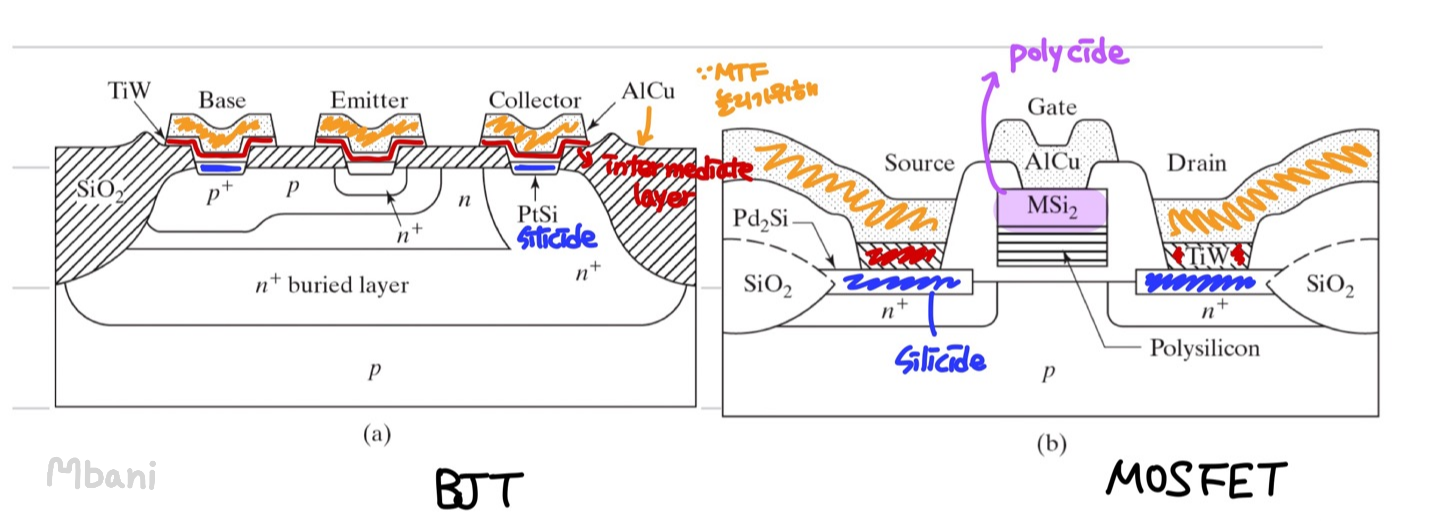

- 일렉트로마이그레이션

원자는 전자 운동량 전달로 인해 금속 필름에서 움직입니다.

이때 고전류 밀도 상황에서 금속 원자의 이동으로 인한 상황의 일렉트로마이그레이션호출됩니다.

빈 공간은 개방 회로를 형성하고 금속 더미(힐록)는 단락을 형성합니다.생성

파일업이 증가함에 따라 금속선이 단락되는 현상은 아래 그림에서 확인할 수 있습니다.

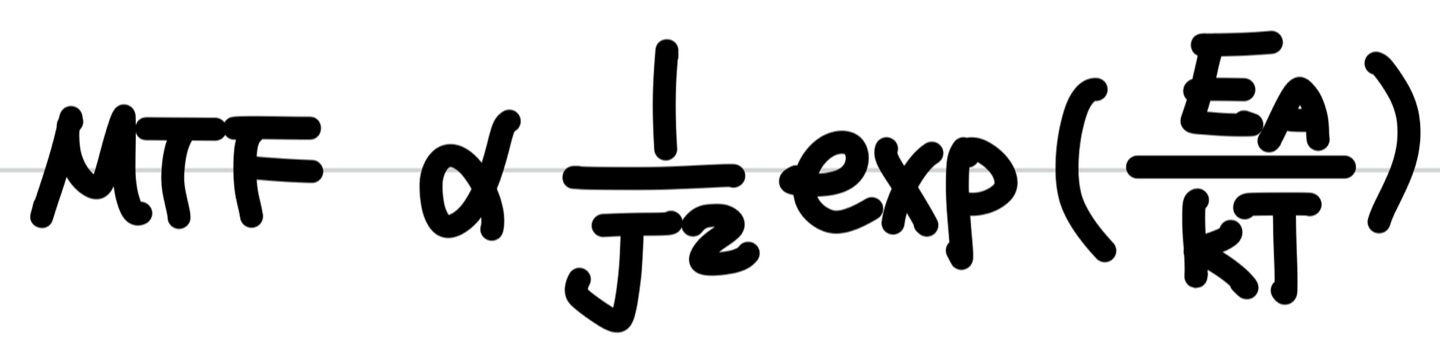

일렉트로마이그레이션으로 인해 평균 고장 시간(MTF)실험적으로 경화제 밀도 J 및 온도와 연결됩니다.

Al 일렉트로마이그레이션을 제거하기 위한 솔루션으로,

Cu 또는 Cu와 같은 중금속을 소량 첨가하십시오.이렇게 하면 이런 일이 발생하지 않도록 방지할 수 있습니다.

스퍼터 증착의 경우 Al 95%, Cu 4%, Si 1%를 사용하면 큰 효과를 얻을 수 있다.

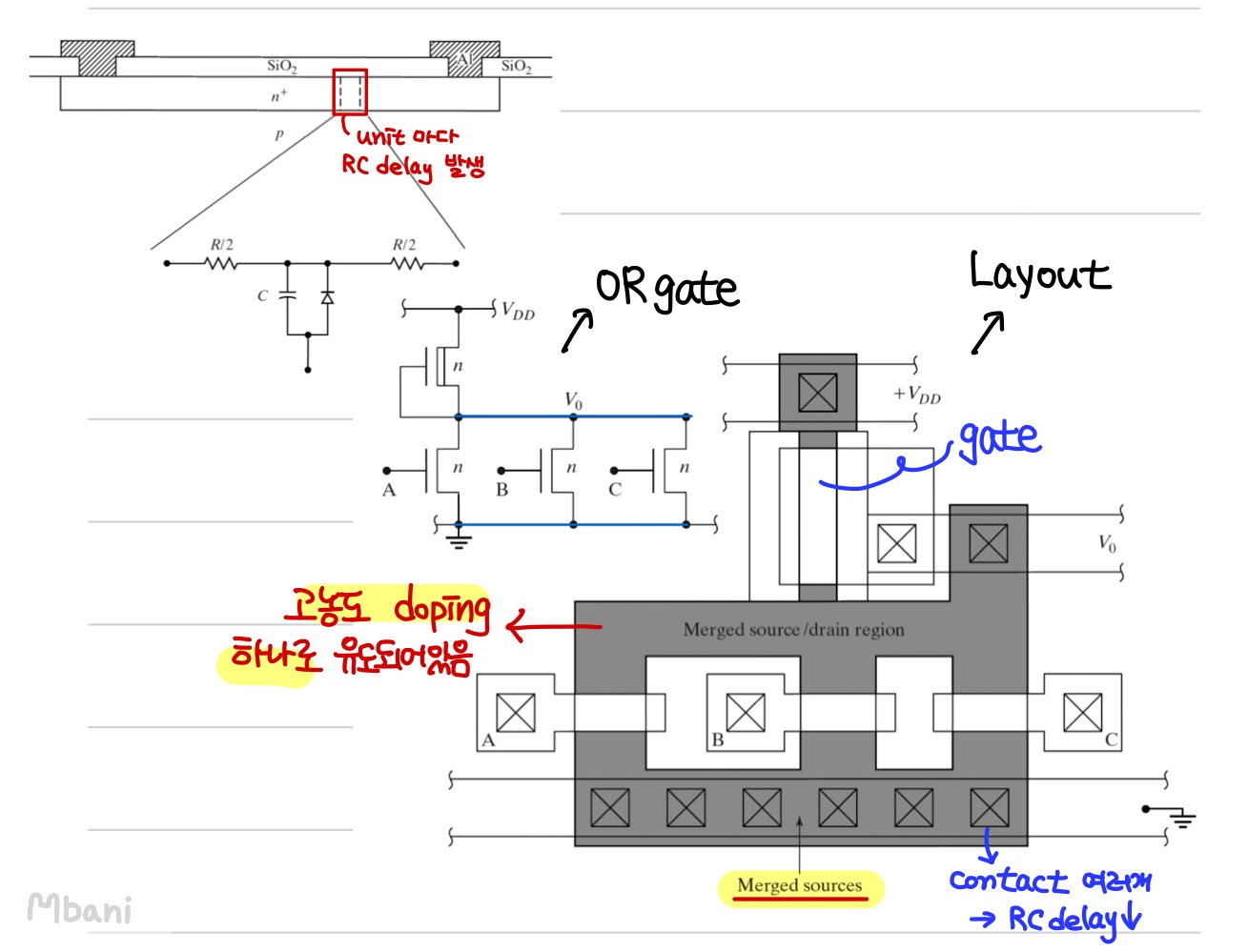

< Diffuse Verbindungen >

확산 라인이 길면 RC 지연이 커집니다.

RC 시간은 작동 주파수를 제한합니다.줄여야 합니다.

일정한 저항을 줄이기 위해 다중 접점이 사용됩니다.

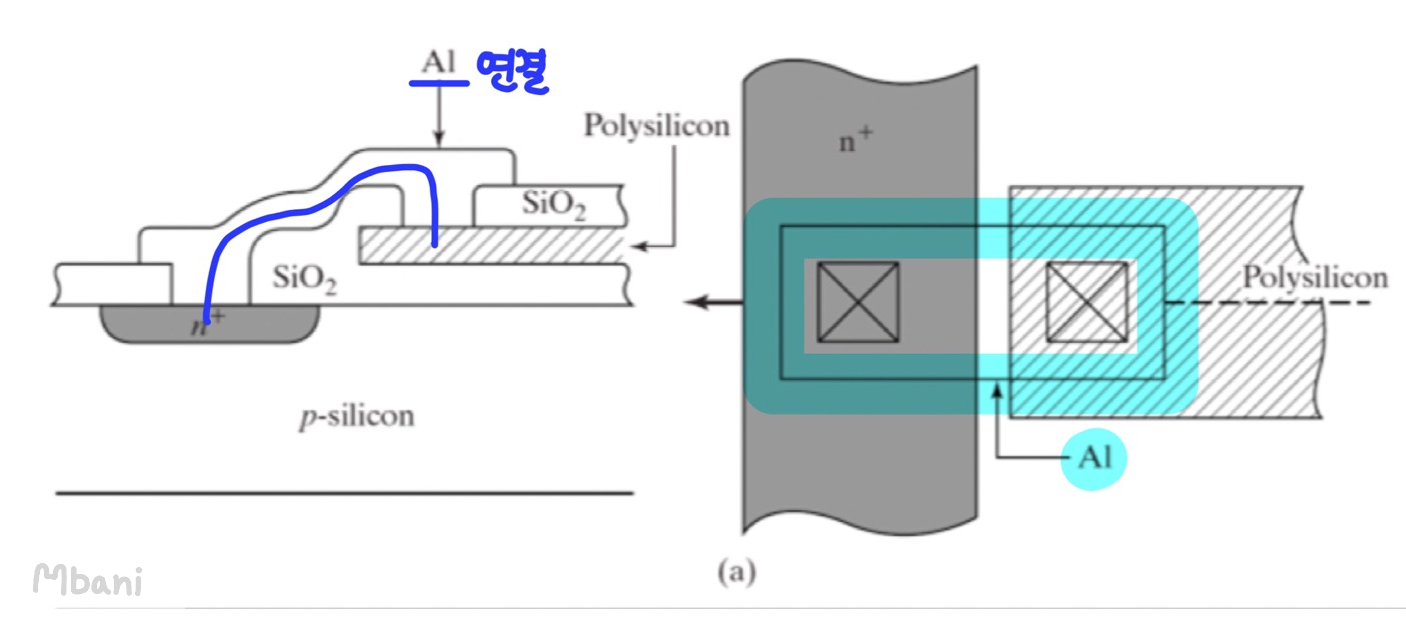

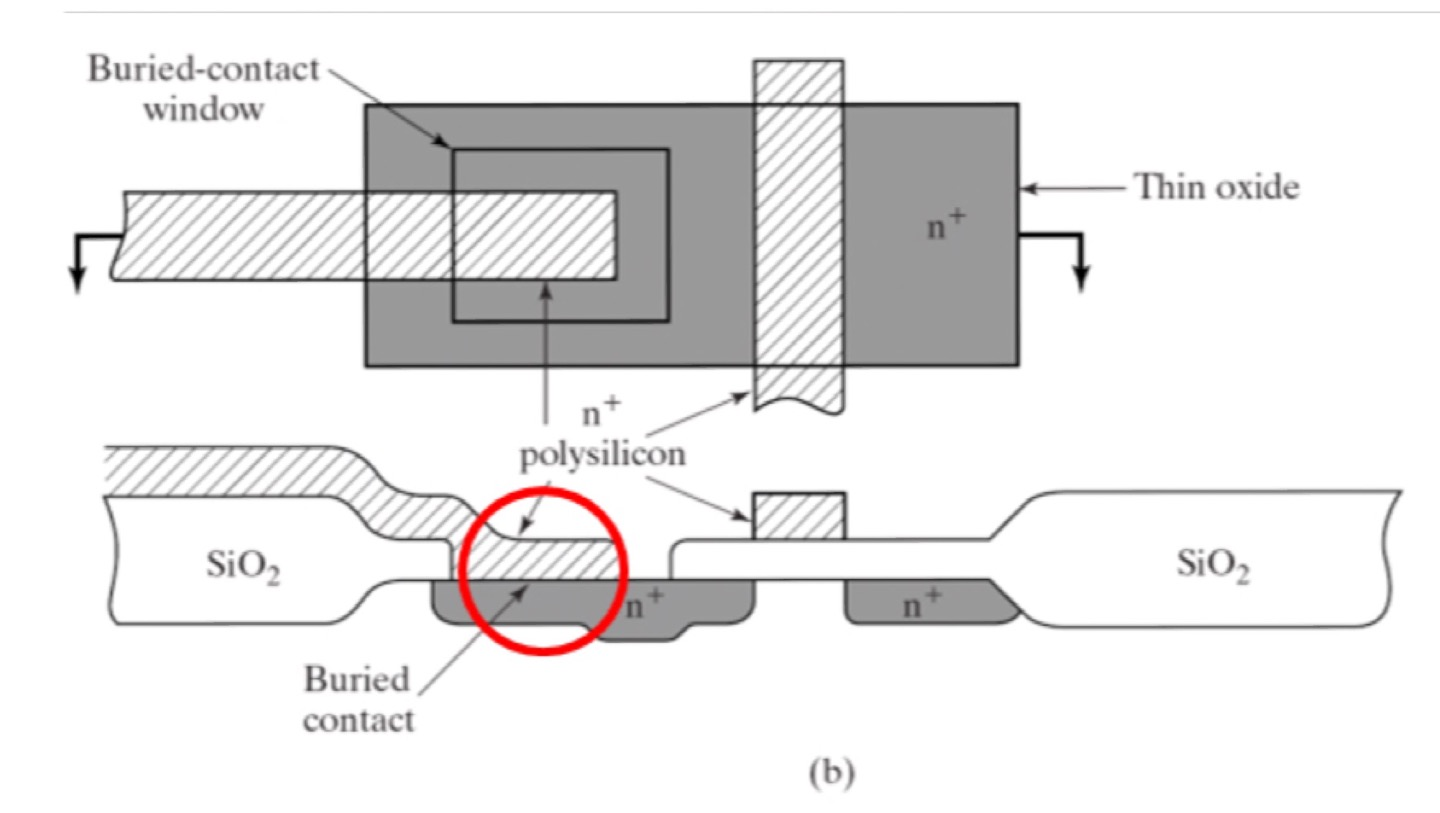

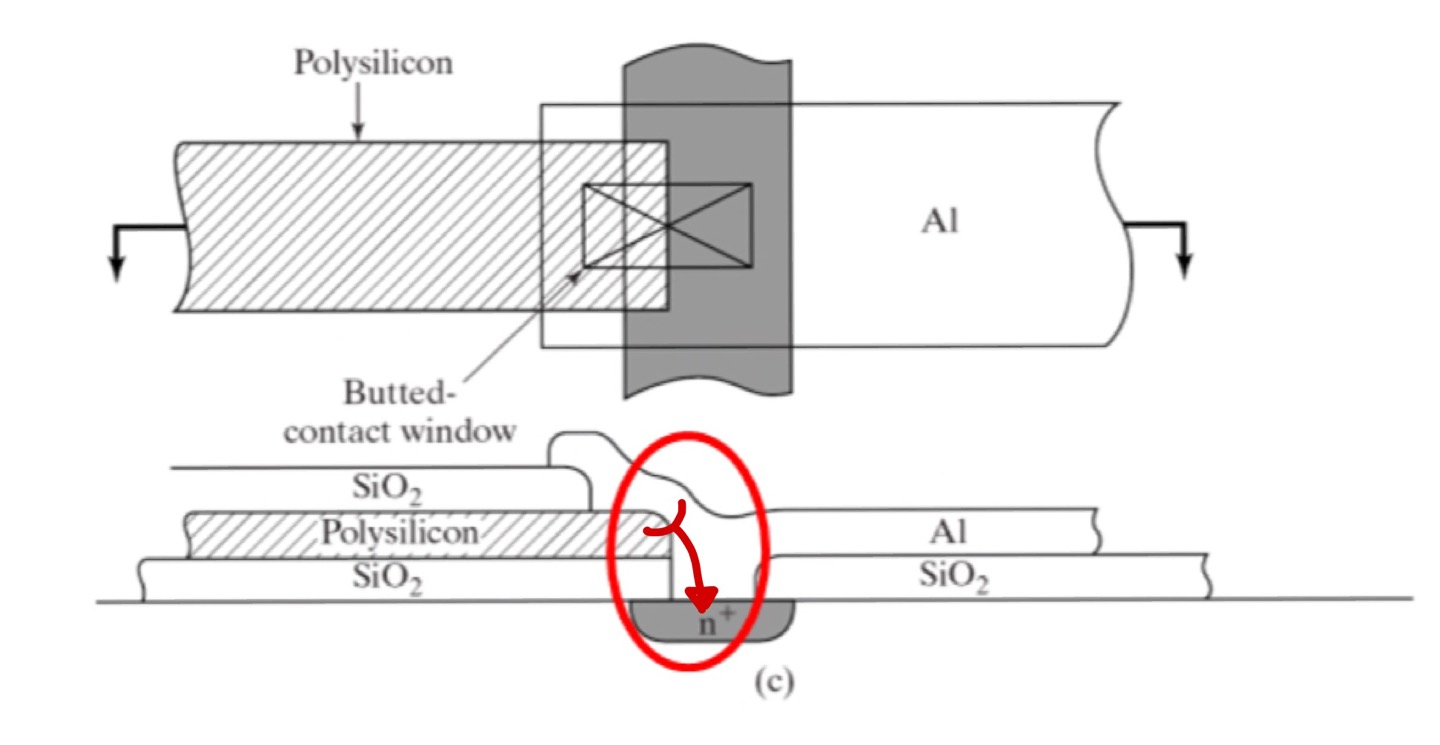

- Poly-Si 및 n+ 확산 연결

위 사진은 옴 접촉이 없는 접촉 스파이크 문제발생할 수 있습니다.

이것을 해결하기 위해 매몰된 접촉 확산으로 직접 결합된 블록 폴리실리콘 5월.

이 경우 직접 연결은 Al이 아니므로 일시적인 피킹이 형성되지 않습니다.

마스크를 재사용해야 하므로 공정 비용이 증가합니다.

이러한 문제는 Al 오버랩에 의한 맞대기 접촉을 형성할 수 있습니다.

- 실리사이드, 폴리사이드, 살리사이드

하나) 실리사이드 : Si와 복합화된 광범위한 금속을 말합니다.

장점으로 낮은 접합 스파이킹 및 시트 저항그것은.

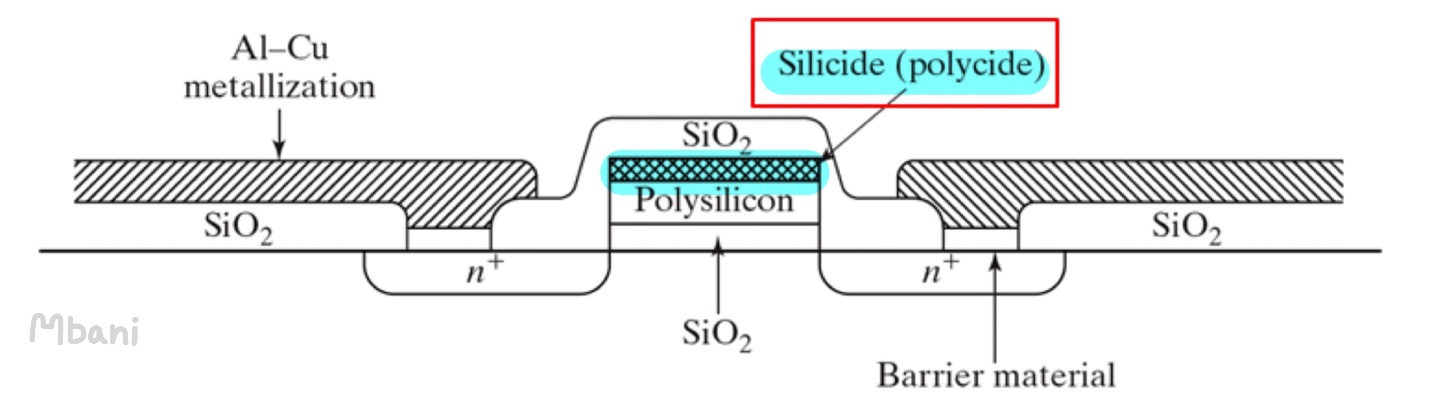

2) 폴리사이드 : poly-Si 게이트에 형성된 실리사이드를 말합니다.

600-1000℃로 가열하면 15-50uΩ-cm의 낮은 저항을 형성합니다.

삼) 살리사이드 : 자체 서명된 실리사이드.

소결하는 동안 실리사이드는 금속과 실리콘 또는 폴리실리콘 사이의 접촉 영역에서만 형성됩니다.

마스크 없이 접촉 부위만 가열하면 Salicide가 자동으로 형성된다.

즉, 이들 물질은 Al 스파이킹을 방지하고 반응성 부분만 화합물로 사용하고 나머지는 선택적으로 날려버린다.

- 장벽 금속 및 다층 접점

Al과 실리사이드와의 직접적인 접촉은 피팅(pitting) 및 스파이킹(spiking) 문제를 야기합니다…

Si 확산을 방지하는 가장 효과적인 방법은

금속(TiW) 접착층을 사용한 고성능.만들 수 있습니다.

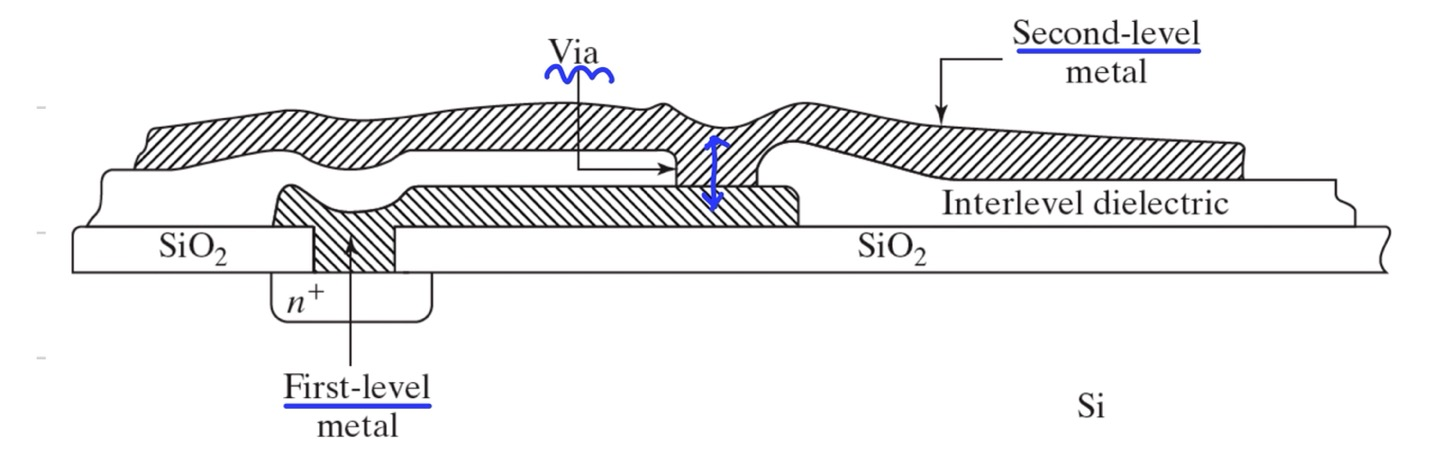

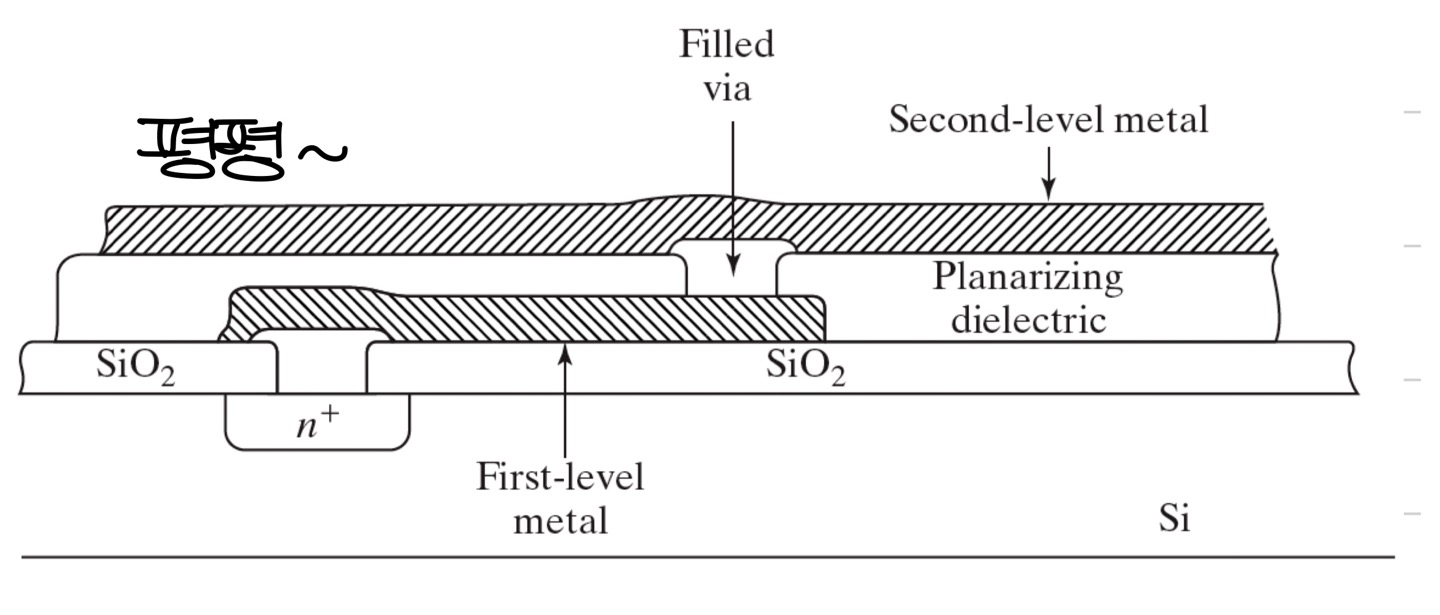

< Mehrebenenmetallisierung >

단일 금속 레벨이 전체를 제공하지 않기 때문에 poly-Si 레벨의 2/3가 각 층 위에 금속화됩니다.

이 수준 배선 및 적절한 전력 분배 제공하다.

기본 다단계 금속화는 다음과 같습니다.

– 1차 금속 레벨의 증착 및 구조화

-> 첫 번째 레이어의 평면 사이에 유전체 증착

-> 유전체 층은 우수한 스텝 커버리지를 제공하고 매끄러운 토폴로지를 돕습니다.

-> 금속화 및 구조화의 2단계 -> …

– 수업 후 평탄화 금속화로 평탄화. 고평면층의 CMP사용

– Via(W)에 Filling을 사용한다.

– Dielectric Deposition -> Metallization -> CMP 공정 순으로 진행

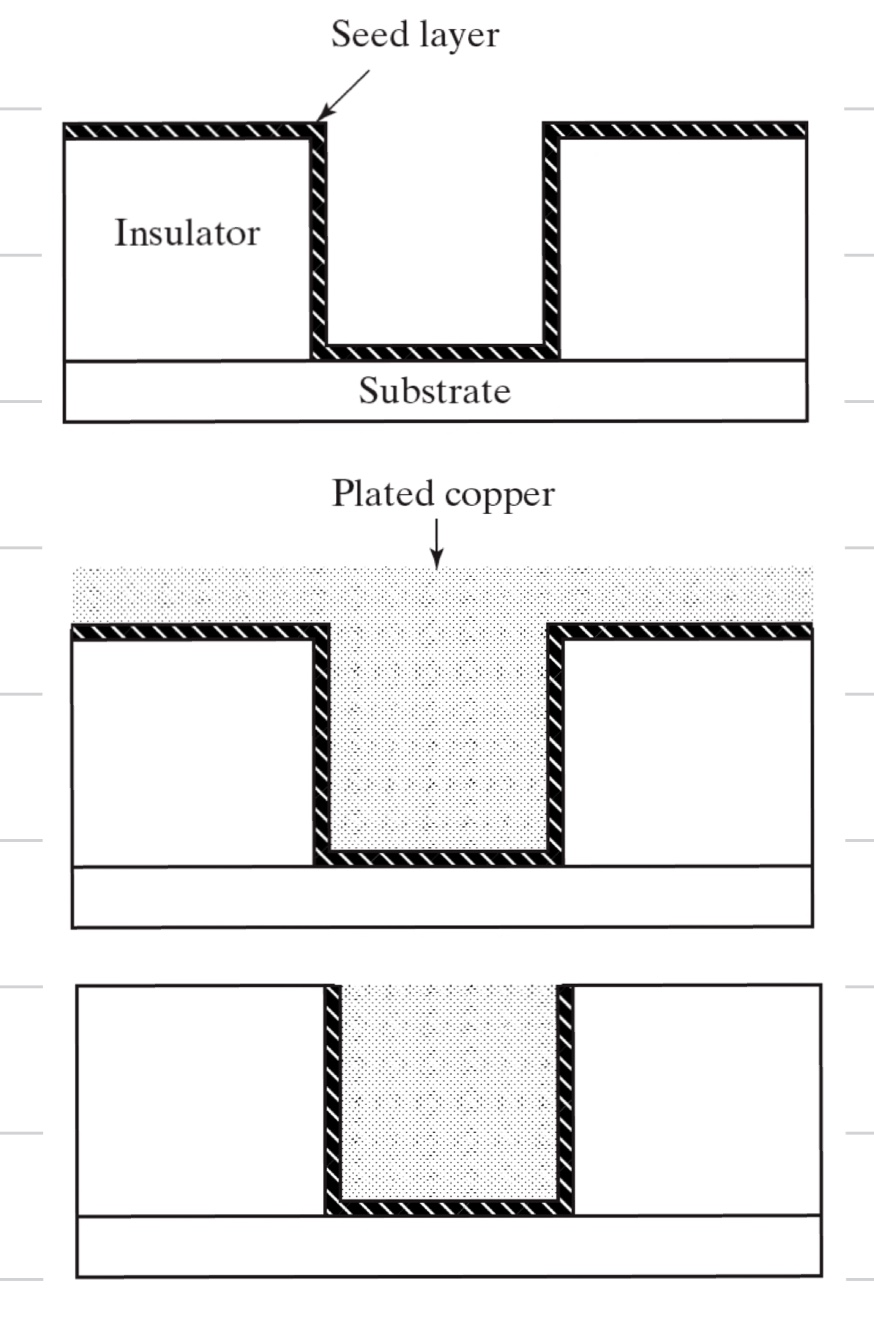

- 아연 도금 구리 연결

Cu는 낮은 저항, 저렴하고 대량이해합니다

Si에서 깊은 수준의 불순물 및 빠른 확산따라서 Si 기판과 소자의 오염에 주의할 필요가 있다.

또한 건식 에칭은 허용되지 않습니다.가능하면 첨가제 코팅 기술을 사용해야 합니다.

구리 도금 절차는 다음과 같습니다.

– 종자층 증착(보호용)

-> PR 증착 및 마스크 패터닝

-> 웨이퍼 상의 코팅 시스템(Cu 용액)

-> 커버 레이어 제거

이 공정은 평탄도가 부족하기 때문에 주로 Cu를 형성하기 위해 다음과 같은 다마신 공정이 사용됩니다.

- 다마스커스 코팅:

다마신 공정에서는 Si 이산화물과 같은 절연층이 기판 표면에 도포됩니다. Cu로 입금하는 방법보지마.

표준 포토리소그래피는 원하는 상호 연결 패턴을 생성하는 데 사용됩니다.

소송 절차) Si 기판 SiO2 증착 후 seed layer 증착

-> 전기화학적 증착에 의한 Cu 도금

-> CMP로 윗면을 평평하게 함

이 과정으로 CuSi와 Si 사이의 확산 방지, Void가 발생해도 전기적 연결 끊김 방지, 평탄성우수하다작동합니다

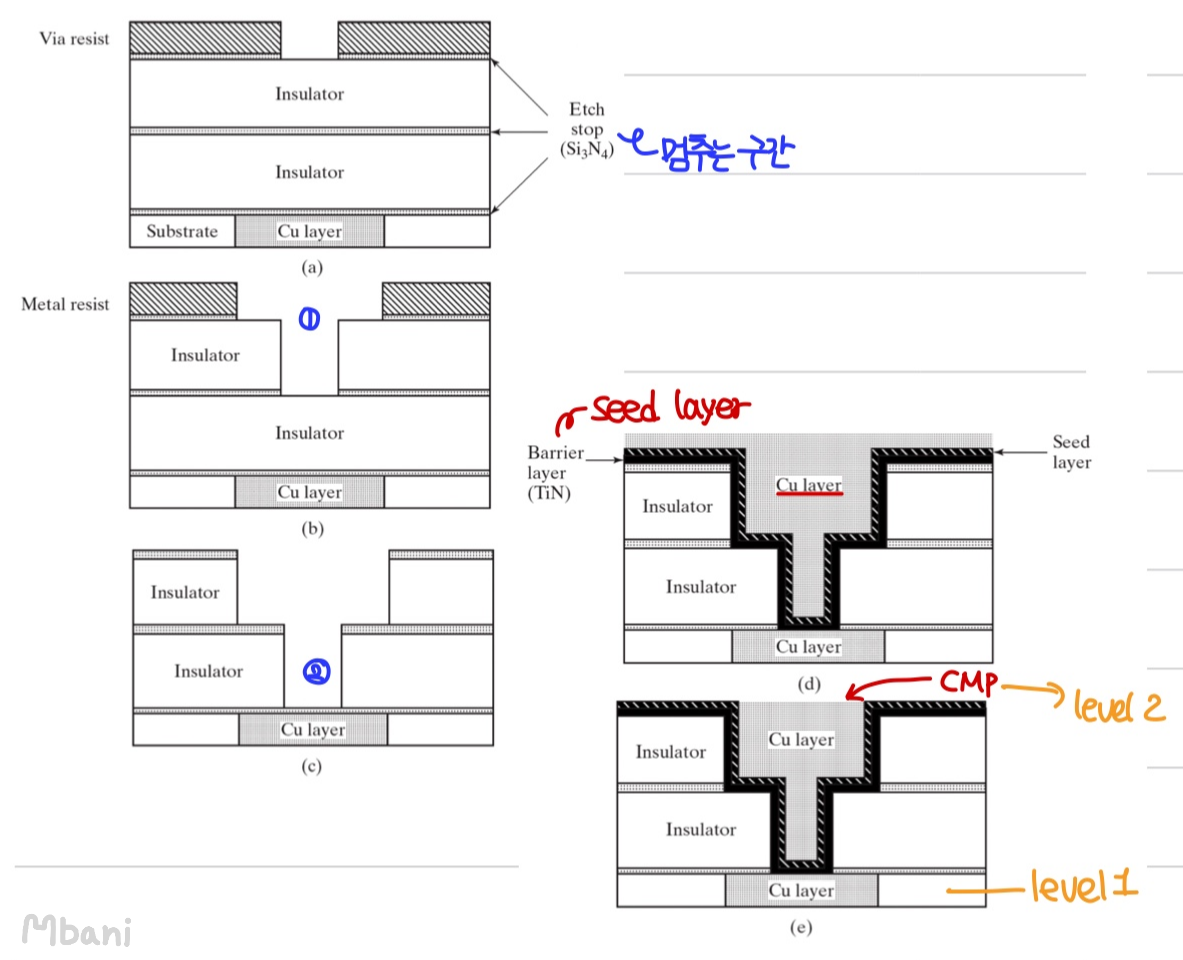

- 이중 다마스크 구조

연결 라인과 비아는 동시에 Cu로 만들어집니다.이런 식으로 우리는 damascene 프로세스를 두 번 사용합니다.

오늘의 기사는 여기!

다음이 반도체 공정과 응용에 대한 마지막 포스팅이 될 것 같습니다..!!

감사해요!